Copyright ©1999-2000 by X Engineering Software Systems Corporation.

All XS-prefix product designations are trademarks of XESS Corp.

All XC-prefix product designations are trademarks of Xilinx.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America.

### Limited Warranty

XSV BOARD V1.0 MANUAL RELEASE DATE: 9/24/2000

### Table of Contents

|     | mited Warranty | . ′ |

|-----|----------------|-----|

|     |                |     |

| Dro | inarios        |     |

|     | Ethernet PHY                              | 20 |

|-----|-------------------------------------------|----|

|     | Expansion Headers                         | 23 |

|     | Pushbuttons and Eight-Position DIP Switch | 25 |

|     | Digit and Bargraph LEDs                   | 27 |

|     | PS/2 Port                                 | 28 |

|     | USB Port                                  | 29 |

|     | Parallel Port                             | 30 |

|     | Serial Port                               | 31 |

|     | Xchecker Interface                        | 32 |

|     | Power Connectors                          | 33 |

| XSV | V Pin Connections                         | 34 |

| XSV | V Schematics                              | 35 |

|     |                                           |    |

# 2 XSV Overview

The XSV Board brings you the power of the XILINX Virtex FPGA embedded in a framework for processing video and audio signals. The XSV Board has a single Virtex

| > | Video decoder that accepts NTSC/PAL/SECAM signals through an RCA jack or S- |

|---|-----------------------------------------------------------------------------|

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

|   |                                                                             |

١

Your next step is to select the parallel port that your XSV Board is connected to using the

| Flash RAM | Virtex   | XC95108    |

|-----------|----------|------------|

| Pin       | FPGA Pin | CPLD Pin   |

| /RESET    | N/A      | <b>3</b> 3 |

### SRAM Banks

| Direct  | RAMDAC | Virtex   | LXT970A  |

|---------|--------|----------|----------|

| VGA Pin | Pin    | FPGA Pin | Function |

|         | D1     | 41       |          |

FPGA and the CPLD. The FPGA acts as a MAC (media access controller) and manages

The CPLD also gets receives the status outputs from the PHY chip that normally drive LEDs. The outputs are active-low and indicate when 100 Mbps operation is selected

| LXT970A<br>Pin | Virtex<br>FPGA Pin | XC95108<br>CPLD Pin | RAMDAC |

|----------------|--------------------|---------------------|--------|

| /LEDS          |                    | 1                   |        |

| /LEDR          |                    | 95                  |        |

| /LEDT          |                    | 96                  |        |

| /LEDL          |                    | 97                  |        |

| /LEDC          |                    | 99                  |        |

| Expansion | Virtex    | Virtex    | SRAM     |

|-----------|-----------|-----------|----------|

| Connector | FPGA Pin  | FPGA Pin  | Function |

| Pin       | to Left   | to Right  |          |

|           | Connector | Connector |          |

| The table below lists the connections from the FPGA and CPLD to the switches. The DIP |

|---------------------------------------------------------------------------------------|

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

Virtex XC95108 Flash RAM

FPGA Pin CPLD Pin Function

XSV BOARD V1.0 MANUAL 27 9/24/2000

| LED | Virtex   | XC95108  | Flash RAM |  |  |  |

|-----|----------|----------|-----------|--|--|--|

|     | FPGA Pin | CPLD Pin | Function  |  |  |  |

| SL5 | 138      | 37       | D5        |  |  |  |

XSV BOARD V1.0 MANUAL 9/24/2000

XC95108

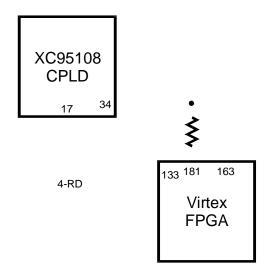

If you want to access the JTAG port of the FPGA, all the requisite pins are already connected to the Xchecker interface except for TDO. The TDO pin of the FPGA connects to pin 34 of the CPLD, so you must route the signal through the CPLD and onto the RD pin of the Xchecker interface (which the Xchecker uses for TDO). You must also make sure that pins 133 and 163 on the FPGA are tristated in your design or else they will override TDO.

## A

## XSV Pin Connections

The following tables list the pin numbers of the Virtex FPGA and the XC95108 CPLD along with the pin names of the other chips that they connect to. These connections correspond with the pin assignments in the user-constraint files VIRTEX.UCF and CPLD.UCF.

| Connections Between the Virtex FPGA and the Other XSV Board Components4 |        |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

|-------------------------------------------------------------------------|--------|---------|-----------|----------|-------|--------------|----------|----------|--------------|-----|------|-----|----------|--------|-------|----------|

|                                                                         |        | XC95108 |           |          | Flash |              | Video    |          |              |     |      |     | Parallel | Serial | Prog. |          |

|                                                                         | FPGA   | CPLD    | LEDs      | Switches | RAM   | Ethernet     | Decoder  | RAMDAC   | Codec        | RAM | PS/2 | USB | Port     | Port   | Osc.  | Xchecker |

| 1                                                                       | GND    |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 2                                                                       | TMS    | 35      | S3 (left) |          | D3    |              |          |          |              |     |      |     |          |        |       | TMS      |

| 3                                                                       |        |         |           |          |       |              |          |          | MCLK         |     |      |     |          |        |       |          |

| 4                                                                       |        |         |           |          |       |              |          |          | LRCK         |     |      |     |          |        |       |          |

| 5                                                                       |        |         |           |          |       |              |          |          | SCLK<br>SDIN |     |      |     |          |        |       |          |

| 6<br>7                                                                  |        |         |           |          |       |              |          |          | SDOUT        |     |      |     |          |        |       |          |

| 8                                                                       | GND    |         |           |          |       |              |          |          | 30001        |     |      |     |          |        |       |          |

| 9                                                                       | OND    |         |           |          |       |              |          |          |              |     |      | VM  |          |        |       |          |

| 10                                                                      |        |         |           |          |       |              |          |          |              |     |      | VP  |          |        |       |          |

| 11                                                                      |        |         |           |          |       |              |          |          |              |     |      | RCV |          |        |       |          |

| 12                                                                      |        |         |           |          |       |              |          |          |              |     |      | /OE |          |        |       |          |

| 13                                                                      |        |         |           |          |       |              |          |          |              |     | CLK  | VPO |          |        |       |          |

| 14                                                                      | GND    |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 15                                                                      | VCCO   |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 16                                                                      | VCCINT |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 17                                                                      |        |         |           |          |       |              | _        |          |              |     | DATA | VMO |          |        |       |          |

| 18                                                                      |        |         |           |          |       | FDS/MDIN     | <b>]</b> |          |              |     |      |     |          |        |       |          |

| 19<br>20                                                                |        |         |           |          |       | MDC<br>MDIO  |          |          |              |     |      |     |          |        |       |          |

| 21                                                                      |        |         |           |          |       | CRS          |          |          |              |     |      |     |          |        |       |          |

| 22                                                                      | GND    |         |           |          |       | CNS          |          |          |              |     |      |     |          |        |       |          |

| 23                                                                      | OND    |         |           |          |       | COL          |          |          |              |     |      |     |          |        |       |          |

| 24                                                                      |        |         |           |          |       | TRSTE        |          |          |              |     |      |     |          |        |       |          |

| 25                                                                      |        |         |           |          |       | TxEN         |          |          |              |     |      |     |          |        |       |          |

| 26                                                                      |        |         |           |          |       | RxDV         |          | RS2      |              |     |      |     |          |        |       |          |

| 27                                                                      |        |         |           |          |       | TxERR        |          |          |              |     |      |     |          |        |       |          |

| 28                                                                      |        |         |           |          |       | RxERR        |          | RS1      |              |     |      |     |          |        |       |          |

| 29                                                                      | GND    |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 30                                                                      | VCCO   |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 31                                                                      |        |         |           |          |       | TxD4         |          | RS0      |              |     |      |     |          |        |       |          |

| 32                                                                      | VCCINT |         |           |          |       | D D4         |          |          |              |     |      |     |          |        |       |          |

| 33                                                                      |        |         |           |          |       | RxD4         |          | D7       |              |     |      |     |          |        |       |          |

| 34<br>35                                                                |        |         |           |          |       | RxD3<br>RxD2 |          | D7<br>D6 |              |     |      |     |          |        |       |          |

| 36                                                                      |        |         |           |          |       | RxD2<br>RxD1 |          | D6<br>D5 |              |     |      |     |          |        |       |          |

| 37                                                                      | GND    |         |           |          |       | ועגטו        |          | טט       |              |     |      |     |          |        |       |          |

| 38                                                                      | SIND   |         |           |          |       | RxD0         |          | D4       |              |     |      |     |          |        |       |          |

| 39                                                                      |        |         |           |          |       | TxD3         |          | D3       |              |     |      |     |          |        |       |          |

| 40                                                                      |        |         |           |          |       | TxD2         |          | D2       |              |     |      |     |          |        |       |          |

| 41                                                                      |        |         |           |          |       | TxD1         |          | D1       |              |     |      |     |          |        |       |          |

| 42                                                                      |        |         |           |          |       | TxD0         |          | D0       |              |     |      |     |          |        |       |          |

| 43                                                                      | VCCINT |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 44                                                                      | VCCO   |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |

| 45                                                                      | GND    |         |           |          |       |              |          |          |              |     |      |     |          |        |       |          |